## The COTS Technology Authority EMBEDDED SYSTEMS VOLUME 2 NUMBER 4 WINTER 2006

IN THIS ISSUE:

## Chris A. Ciufo

Remembering December 7

## Joe Paylat

MicroTCA in the military

## **Hermann Strass**

MAE Show, Europe

WWW.MIL-EMBEDDED.COM

## DoD addresses IPv6 But is the Internet ready?

Mil systems lose their insecurities Java's the answer to legacy portability

PM40048627

PRST STD U.S. POSTAGE PAID BLAINE, WA PERMIT NO. 226

©2006 OpenSystems Publishing. Not for distribution.

## Keep your SPARC supply lines open.

USP Ile™ VMEbus Computer

650-MHz UltraSPARC<sup>®</sup> IIi+ CPUs 4GB SDRAM

Optional TGA3D+™ and TGA-100™ graphics support Gigabit Ethernet

PCI expansion to four slots

Four serial ports

VME Interface - VME64X via Tundra Universe II

PS/2 or USB keyboard/mouse

Solaris™ 8/9/10 Support

Two UltraSPARC IIIi

1.2 GHz CPUs

4GB 266DDR SDRAM

per CPU, 8GB total

Optional TGA3D+

and TGA-100 graphics

Gigabit Ethernet port

One 64-bit/66-MHz PMC slot

Up to four PMC expansion slots

Dual FC-AL/SCSI ports

Additional VME-backplane access

Up to 30G shock

Solaris OS Support

Do your mission critical applications depend on SPARC/ Solaris solutions? Many suppliers are ending their support for SPARC-based single board computers. Not Themis. Themis is committed to providing its customers and industry with high performance UltraSPARC VMEbus single board computers.

Themis has solutions. We are committed to providing you with the industry's widest breadth of high performance UltraSPARC-based VME single board computers. To support thousands of Solaris platform solutions for the most demanding mission critical applications.

Don't be forced into changing your computing platform today. Extend the life of your system and gain control over your program lifecycle and budget with Themis SPARC solutions.

Themis is keeping the SPARC supply lines open so call Themis today.

www.themis.com (510) 252-0870

Transformational.

RSC# 2 @www.mil-embedded.com/rsc

Take a closer look at your encryption.

## Are you getting the protection you need?

Members of the Sierra™ family of encryption modules are easily integrated into communications devices of all kinds. Sierra encrypts classified information, processes data at a higher speed, is extremely power efficient, and allows modules to be reprogrammed as missions change.

It's benefits like these that led the U.S. Department of Defense to select Sierra II for one of the most important communications programs in recent history. Sierra II has been chosen to encrypt 100 percent of the radios under Cluster 1 of the U.S. Joint Tactical Radio System program.

www.harris.com

RF Communications

Government

Broadcast

Microwave

assuredcommunications™

# EMBEDDED SYSTEMS

**VOLUME 2** NUMBER 4

www.mil-embedded.com

## **DEPARTMENTS**

## **Industry Analysis**

- 8 MicroTCA: High performance in a small package

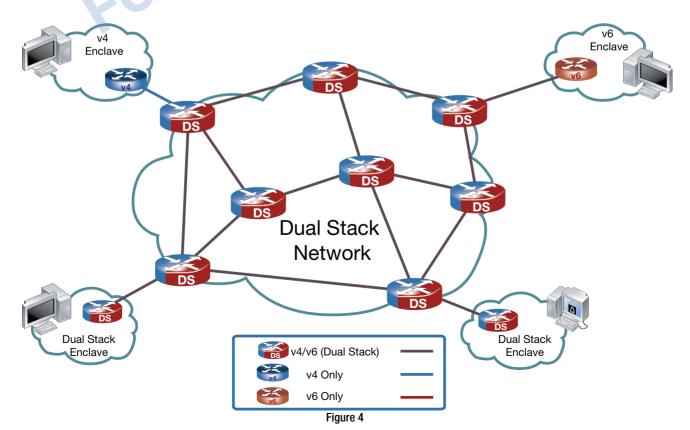

- **Embedded computing systems take IPv6** 10 switches to heart By Duncan Young

- Special Report: Military Technology in Europe: 14 MAE Show, Ascot (UK) Bv Hermann Strass

## **Departments**

- **Editor's Choice Products**

- 46 **New Products** By Sharon Schnakenburg

## **Crosshairs Editorial**

- December 7 still lives in infamy By Chris A. Ciufo

- Advertiser Index

## **E-CAST**

Mapping Multi-function Radar Algorithms Across a VPX-REDI System

January 25, 2 p.m. EST

www.opensystems-publishing.com/ecast

## **COVER**

COTS electronics and software are now routinely used in avionics applications, but the need for safety-critical software in mission-critical applications remains acute. From operating systems to Java to IPv6, software is increasingly becoming robust enough for use in aircraft like this F-16 Fighting Falcon or the KC-135 tanker that's refueling it. (Image courtesy of US Air Force; photographed by Senior Airman Brian Ferguson.)

© Military Embedded Systems

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

Published by:

**SOFTWARE:** More OS options open up

- Java technology trends offer renewed promise for portable embedded applications By Dave Wood, Aonix

- Custom real-time kernels versus COTS Real-Time Operating Systems By Alex Polmans and David Mosley, DDC-I, Inc.

**TECHNOLOGY**: Feeling confident: Mil systems lose their insecurities

- 30 Building secure software: Your language matters! By Robert B.K. Dewar, PhD, AdaCore and Roderick Chapman, PhD, Praxis High Integrity Systems

- 34 IPv6 — The next-generation Internet By Brad Ryan, Juniper Networks

- PRODUCT GUIDE: MPC7448 PowerPC SBCs 42 and Systems

www.mil-embedded.com/eletter

Adaptive meshing helps Army develop **Future Combat Systems**

By Jerry Fireman, representing Fluent Inc. and Benét Labratories

Using resource partitioning to build secure, survivable military systems

By Paul N. Leroux and Kerry Johnson, QNX Software Systems

Using your existing test and measurement platform to perform Serial RapidIO protocol analysis

By Barbara Aichinger, FuturePlus Systems

Visit us online for the complete list of articles

## Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

**Industry news:**

Read: www.mil-embedded.com/news

Submit: www.opensystems-publishing.com/news/submit

Submit new products:

www.opensystems-publishing.com/vendors/submissions/np

4 / FALL 2006

MILITARY EMBEDDED SYSTEMS

©2006 OpenSystems Publishing. Not for distribution.

## **Advertiser** Information

### Page/RSC# Advertiser/Product description 45 ACCES I/O - Analog, Digital, Relay, and Serial I/O Products

Advantech - Rugged Solutions 48

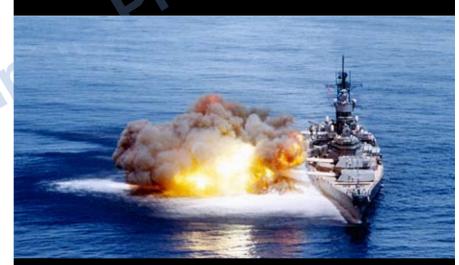

Annapolis Micro Systems - FPGA Systems 53

Arrow Electronics - MicroTCA Communications Servers 11

Concurrent Computer Corporation – Dual-core Processors 52

56 Curtiss Wright - VPX, VPX-REDI

9 DIGITAL-LOGIC - MPCX48, MPCX47

46 Embedded Planet - EP8548A Serial RapidIO AMC

26 **Excalibur Systems - Avionics Communications**

GE Fanuc - Q104-1553 55

35 General Micro Systems - V394, CC61X

21 General Standards Corporation - Analog, Digital, and

Serial I/O Products

Harris RF Communications Division - Sierra Encryption Modules 3

Hybricon - Ruggedized COTS Solutions 49

15 Hypertronics - Connectors, Solutions

7 ICS Sensor Processing - ICS-8550

5 Intel - Intel Solutions

41 Jacyl Technology - Project Solutions

Merlin – Product Obsolescence Solutions 44

MPL AG - Rugged Embedded Computers 39

50 North Atlantic Industries - Military Power Supplies

Phoenix International - Data Storage Modules 13

RTD Embedded Technologies – PC/104 Modules and Systems 28

32 Sealevel Systems - Relio Computing Solutions

TEWS Technologies - COTS I/O Solutions 6

Thales - PowerMP6 27

Themis Computer - SPARC SBCs 2

Tri-M Systems - 100 MHz PC/104 Module 17

Tri-M Systems - Distribution Services 19

51 VMETRO - High-speed Data Recording

with Outstanding Software Support.

**CPU Carrier** IP and PMC Carriers Ethernet Communication CAN Bus Field Bus Digital I/O Analog I/O PC Card/CardBus

**Motion Control**

VxWorks Linux

Windows LynxOS

TEWS TECHNOLOGIES LLC: 9190 Double Diamond Parkway, Suite 127- Reno, NV 89521/USA Phone: +1 (775) 850 5830 - Flax: +1 (775) 201 0347 - E-mail: utassales@firest.com

TEWS TECHNOLOGIES GmbH: Am Bahnhof 7 - 25469 Halstences / Germany Phone: +49 (0)4101-4058-0-Fax: +49 (0)4101-4058-19-E-mail: info@tows.com

## Military embedded systems

AN OPENSYSTEMS PUBLICATION

## Military and Aerospace Group

DSP&FPGA Product Resource Guide

DSP-FPGA.com

DSP-FPGA.com E-letter

Military Embedded Systems

Military Embedded Systems E-letter

PC/104 & Small Form Factors

PC/104 & Small Form Factors E-letter

PC/104 & Small Form Factors Resource Guide

VME and Critical Systems

VME and Critical Systems E-letter

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Senior Editor (columns) Terri Thorson

tthorson@opensystems-publishing.com

Assistant Editor Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

Hermann Strass **European Representative**

hstrass@opensystems-publishing.com

Steph Sweet Art Director

**Senior Web Developer**

**Graphic Specialist** David Diomede

Circulation/Office Manager Phyllis Thompson

subscriptions@opensystems-publishing.com

## OpenSystems Publishing

### Editorial/Production office:

16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466

Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

## **Communications Group**

Editorial Director Joe Paylat

Assistant Managing Editor Anne Fisher

Senior Editor (columns) Terri Thorson

Technology Editor Curt Schwaderer

European Representative Hermann Strass

## **Embedded and Test & Analysis Group**

Editorial Director Don Dingee Editorial Director Jerry Gipper Technical Editor Chad Lumsden

Associate Editor Jennifer Hesse

European Representative Hermann Strass

Special Projects Editor Bob Stasonis

## Reprints and PDFs

Becky Mullaney 717-399-1900, Ext. 166

mesreprints@opensystems-publishing.com

ISSN: Print 1557-3222

Military Embedded Systems (USPS 019-288) is published four times a year (Spring, Summer, Fall, Winter) by OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082

Subscriptions are free to persons interested in the design or promotion of Military Embedded Systems. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/year (advance payment in US funds required).

Canada: Publication agreement number 40048627

Return address WDS, Station A PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to Military Embedded Systems 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

## More reasons to choose Radstone.

The one and only ICS-8550.

Designed for high-speed data acquisition applications such as Software Defined Radio, SIGINT, tactical communications and radar, the ICS-8550 XMC module – which is available for both benign and rugged environments – can simultaneously sample two RF/IF inputs at frequencies up to 210 MHz at a resolution of 12 bits.

With the industry-leading Xilinx Virtex-4 FPGA at its heart to deliver unprecedented power and user programmability – and enabling IF/UHF signals to be processed directly on the board itself, freeing the host board for other tasks - the ICS-8550 is truly an ADC module that sets new standards.

And with up to eight lanes of high-speed serial I/O, the ICS-8550 provides the throughput to match its performance and flexibility. Configure it with Radstone's remarkable V4DSP FPGA/PowerPC processor, and the partnership is unbeatable.

Radstone. For when you need more.

RSC# 7 @www.mil-embedded.com/rsc

## MicroTCA: High performance in a small package

By Joe Pavlat

MicroTCA is a new open computing standard developed by PICMG that provides high performance and modularity. However, it is physically small enough to be used in a variety of mobile military applications, including vehicle and airborne platforms. MicroTCA uses the new AdvancedMC mezzanine cards that were originally designed for AdvancedTCA applications but uses them in a different way. AdvancedMC cards provide high performance in a small package. They are fabric-based and can use PCI Express, Ethernet, or RapidIO for high-speed data transfer. They are also fully managed and hot swappable, making them ideal for high-availability applications where systems resources can be made redundant so that cards can fail and the system keeps operating. In MicroTCA, AdvancedMCs (see Figure 1, courtesy of GE Fanuc Embedded Systems) plug directly into the system backplane, whereas they typically plug onto a carrier card in AdvancedTCA applications.

MicroTCA provides a high-performance multiprocessor architecture that supports CISC and RISC processors, DSPs, FPGAs, and network processors simultaneously. Data throughput exceeds 10 Gbps per slot, so MicroTCA is ideal for applications requiring lots of data manipulation and transfer, including voice, image, and radar processing. The MicroTCA backplane supports star, dual star, and full mesh topologies.

The MicroTCA architecture is very scalable. Simplex systems with single resources can be built quite inexpensively and are suitable for applications where low cost is critical and occasional failures can be tolerated. Duplex systems with redundant cards and high-availability software are more complex and expensive, but can offer 5 Nines availability, 99.999 percent uptime.

Military electronic systems designers are rapidly warming to the concept of availability, borrowed from the telecom world where systems are often expected to operate continuously for 30 years or longer. Simple Mean Time Between Failure (MTBF) calculations, which are often little more than an estimate of how often systems might fail, are increasingly viewed as insufficient for the job at hand. The underlying concept of availability is that the system provides redundant hardware and software management such that no single element can be a single point of failure for the entire system. In a highly available system, single elements, payload cards, and power supplies can fail and be replaced at a convenient time without bringing the system down. Because MicroTCA is a switched fabric architecture and not a parallel data bus such as VME or CompactPCI, sys-tems can be designed in a way that a single card failure need not bring the entire system down. The hardware management structure of MicroTCA is largely borrowed from the wellwrung-out AdvancedTCA management architecture. Industry standard highavailability middleware, defined by the Service Availability Forum, can be used.

MicroTCA was originally conceived as a smaller, lower-cost cousin to AdvancedTCA, and telecom was viewed as its primary market. Since the specification has been ratified, a high degree of interest for nontelecom applications has surfaced. Prime among them are military applications. (Refer to our sister publication *PC/104 and Small Form Factors*: "Rugged MicroTCA: A swappable alternative" at www. smallformfactors.com/articles/id/?1861).

While MicroTCA is ruggedized to telecom standards for shock, vibration, temperature, earthquake, and so on, it is not yet ready for the extreme requirements of the mobile military environment. But a number of PICMG member companies

Figure 1

## Industry Analysis \_

are working on developing concepts that range from cocooning a MicroTCA chassis inside an ATR box with shock mounting and conduction cooling (shown in Figures 2 and 3, courtesy of Hybricon Corporation).

At least one PICMG member company is working on metal clamshells that encase AdvancedMC cards and are then rigidly mounted in a special chassis and directly conduction cooled. It is expected that this work will move into PICMG and become a formal specification development activity at the end of 2006. A lot of work remains both in terms of defining the requirements and then designing a so-lution, but the wide range of expertise in PICMG's 300-strong membership will be brought to bear as usual.

Figure 3

Figure 2

You can learn more about MicroTCA and its architecture in another OpenSystems Publishing publication, CompactPCI and AdvancedTCA Systems magazine.

For more information, contact Joe at jpavlat@opensystems-publishing.com.

Editor's Note: As we went to press, Motorola announced \$1.0 million in MicroTCA product sales – a significant milestone event. See www.vmenow.com for more information.

presented by OpenSystems Publishing

## **UPCOMING E-CASTS JANUARY 2007**

Mapping Multi-Function Radar Algorithms Across a VPX-REDI System January 25, 2 p.m. EST Presented by: Mercury Computer Systems

## DID YOU MISS AN E-CAST? DON'T WORRY.

Archived E-casts are at www.opensystems-publishing.com/ecast

www.opensystems-publishing.com/ecast

## **In-Vehicle PCs**

smallest dimensions. fanless, high reliability, rugged design

- VGA, DVI, LVDS, Audio, Video-in

- LAN, COM1, COM2, 6x USB

- Options: WLAN, GPS, GSM, CAN

## MPCX47 (IP65)

- Intel® Pentium® M 738, 1.4GHz

- VGA, DVI, LVDS, Audio, Video-in

- LAN, COM1, COM2, 4x USB, 2x firewire, Digital I/O

- Exchangeable mediapack 40GB automotive HDD 1x CF TypeII

- Options: UPS-battery, preheating, GSM, GPS, WLAN, CAN

Further informations: www.digitallogic.com

DIGITAL-LOGIC offers a wide range of embedded computer boards and systems for stationary and mobile applications.

Advanced Digital Logic Inc. 4411 Morena Blvd. Suite 101 San Diego, CA 92117-4328 Phone +1 858 490 0590 Fax +1 858 490 0599 sales@adlogic-pc104.com www.digitallogic.com

## Field Intelligence By Duncan Young

## **Embedded computing systems** take IPv6 switches to heart

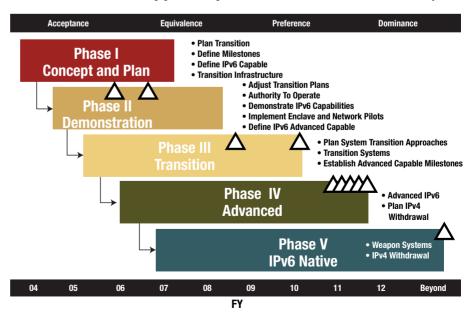

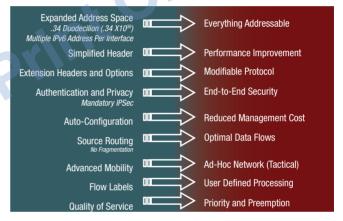

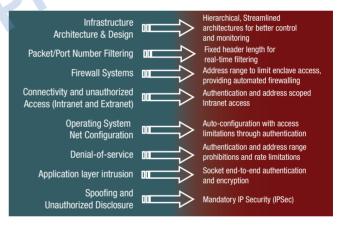

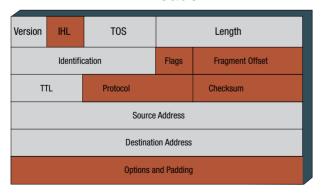

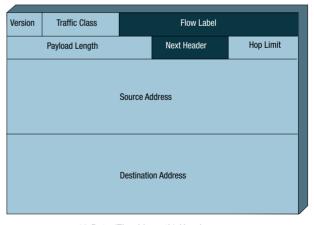

Military operations have seen a massive emphasis shift from the physical domain of the soldier, tank, or combat aircraft to the informational and intelligence domains. This drive toward tactical awareness domination will be the key to the efficiency and speed of military operations in the future networked digital battlefield. Obviously, much enhanced communications capacity and security will be needed at all levels to implement these network-centric operations. This is why IPv6 has been selected as the common future protocol for sharing voice, data, and video across all levels of operations from the soldier and sensors, to weapons platforms, to logistics, to planning and strategic operations.

IPv6 is the foundation of interoperability for the DoD's Global Information Grid (GIG), which uses Internet technology to provide seamless integration of information all the way from an Unmanned Aerial Vehicle (UAV), a helicopter, or a soldier in the field, to the Pentagon and back (known as reachback). IPv6 has been selected now to allow time for the creation of

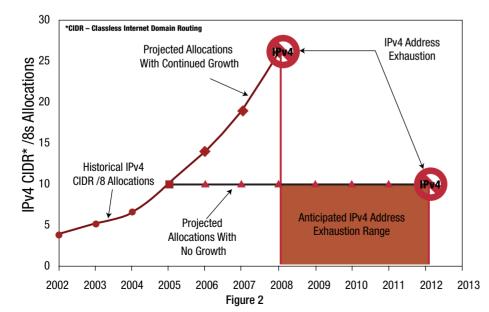

new infrastructure plus the gradual transition IPv4 to IPv6. After many years adoption, IPv4 is finally running out of steam, requiring three major areas of improvement for military applications that are resolved by IPv6:

- Built-in protocol and payload encryption While IPv4 supports some levels of encryption, it is implemented as an add-on rather than an inherent part of its functional capability. The additional encryption support provides military applications with the security needed for the protection of data and command structures, although it requires more processor power within a switch for effective network operation.

- Selectable Quality Of Service (QOS) for different classes of communications – High priority and security are vital for critical applications where real-time response and data integrity must be achieved. Other services may be less time-critical and may not need to rely 100 percent on data integrity. Streaming MPEG video is a good example of such a service where decompression and reconstruction can tolerate some timing jitter and data errors created by transmission through a network.

of legacy systems from ... IPv6 has been selected as the common future of worldwide protocol for sharing voice, data, and video across all levels of operations from the soldier and sensors, to weapons platforms, to logistics, to planning and strategic operations.

■ Much larger addressing range without resorting to address translation - IP was conceived long before the Worldwide Web became the force it is today, resulting in just not enough address space to go around. Current IP addresses have a 32-bit field giving approximately 4.3 billion unique addresses but, because of different classes of address, typically only 3 billion of these are readily available. The number of Internet users is doubling every year and will very soon exceed the number of addresses available. However, Network Address Translation (NAT) is used extensively by local networks and ISPs whereby just one global IP address can be mapped to many local unregistered IP addresses, thus extending the number of potential users to many times that which would be available directly. IPv6's 128-bit address field reduces the need for address translation and would allow a very large user such as the DoD to assign its own unique IP addresses to every intelligent node and subsystem in its entire inventory without NAT.

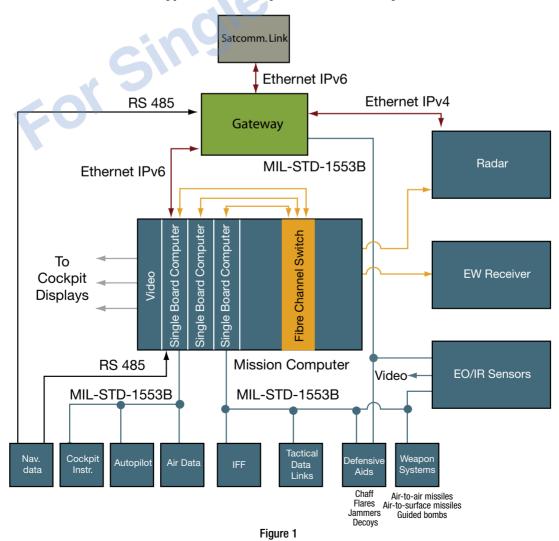

At the heart of almost every operational platform such warships, submarines, armored vehicles, helicopters, combat aircraft and so on - is a combat system or a mission system. In addition, there will be a mix of current and legacy subsystems, weapons, and sensors

attached, using both point-to-point connected (for example, federated) and networked architectures for interconnection. With the exception of a few newly designed platforms, these older platforms are the ones that will present the greatest challenges to the introduction of IPv6 and integration within the GIG. For example, a Naval combat aircraft, such as an F/A-18 Super Hornet, might have sophisticated networked connectivity between its mission computer and its primary sensors and weapons systems using Fibre Channel but may also have many legacy subsystems connected via MIL-STD-1553B. External communications, such as radios, are often limited to voice and a number of highly secure data links used to share data with other aircraft and surface ships within the local tactical environment. Such platform systems typically use unique internal data structures and maintain physical separation of mission data and sensor video. This makes them unsuited to an Internet-like communications environment without extensive modification to their application software packages.

Back in 1981, while people were busy spinning on their heads, Motorola launched VME and left the embedded computing competition flat on its back.

## Now, 25 years later, Arrow Electronics and Motorola are defining the new era in embedded computing with MicroTCA™ solutions.

**MicroTCA communications servers** use a revolutionary system architecture to meet the military's budget requirements and work within an open architecture computing environment. Motorola is recognized for its key role in ushering in this innovative technology. Backed by Arrow's broad line card, technical expertise, services, outstanding integration capabilities, and supply chain solutions, MicroTCA technology reduces the time required to deploy and refresh systems.

**WONN**

Offering the economies of commercial off-the-shelf products and the flexibility of custom solutions, MicroTCA technology co-exists with VME and extends the life of previous investments through:

- · Adherence to standards-based open architecture systems requirements

- Very compact form factor

- Superior chassis flexibility

- Compute density and scalability

- Hot-swappable Advanced Mezzanine Cards

- A common base platform and associated cost savings

Arrow and Motorola—

Defining the New Era in Defense and Aerospace Efficiency

## Development units available.

Call 888-427-2250 or visit www.arrownac.com/NotAPassingTrend to learn why MicroTCA technology is destined to influence embedded computing for a long time to come. Quantities are limited, so call now!

©2006 Arrow Electronics, Inc. Arrow and the Arrow logo are registered trademarks; MOTOROLA and the Stylized M Logo are registered in the US Patent & Trademark Office. PICMG and the PICMG logo are registered trademarks, and MicroTCA is a trademark of the PCI Industrial Computer Manufacturers Group.

## Field Intelligence

## IPv6 gateway

The most likely initial steps will be to incorporate IPv6 by means of a gateway. This will consist typically of an intelligent subsystem incorporating a switch with a high-bandwidth external connection to the GIG. Other connections to the switch will be the platform's sensors and its combat or mission system (Figure 1), offering only filtered views of the total information content available locally. It is likely that in addition to newer subsystems designed specifically with IPv6, many legacy pieces of equipment will be connected to the gateway, probably a mix of older IPv4 systems and subsystems using 100 Mbps or 1 Gbps Ethernet in copper or fiber. Additionally, such a gateway could be used to connect further legacy subsystems using MIL-STD-1553B or RS-485. For these legacy connections, the gateway needs to provide translation and support for the upper layers of the communications model in order to transfer any meaningful information.

Small platforms such as an armored vehicle may have only one gateway; larger platforms such as a Naval vessel may have many.

The ideal way to implement such a gateway is as a COTS-based embedded subsystem with an IPv6-capable Ethernet switch and whatever legacy interfaces might be required to connect to the older subsystems. IPv6 can handle IPv4 traffic through its network though it retains the limitations of IPv4, reducing the need to replace or upgrade every existing subsystem for compliance.

## Platform-level switched fabrics

But Ethernet and IPv6 are not just limited to the interplatform network domain of the GIG. Within platforms, there is growing demand for high-speed switched fabrics typified by Fibre Channel, Serial RapidIO, and PCI Express. These are used to enable data and resource sharing between multiple processors of a mission or combat system and the many subsystems making up the complete platform. These fabrics are usually characterized by their high line speeds (>1 Gbps) and low latency, which are both required for real-time, deterministic operation of the platform's system. Ethernet will have the capability and latency to become a platform's primary switched fabric. This reflects

## **Typical Mission System with Gateway**

## Field Intelligence-

best practice in the commercial and telecommunications worlds, where Ethernet is firmly established as the *de facto* standard.

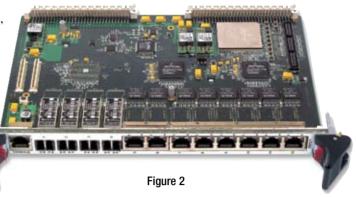

Hence a number of COTS vendors such as Curtiss-Wright Controls Embedded Computing, Radstone, and GE Fanuc Embedded Systems have introduced IPv6-capable Ethernet switches into their product portfolios. These switches offer built-in flexibility to support a number of physical connections and line speeds and include a processor for local network management functions. COTS switches are available in many formats including VME and CompactPCI, both of which are ideal for implementing gateway functions or intraplatform networks in deployed military applications. Typical of these is GE Fanuc's RM921 (Figure 2) managed VME Ethernet switch with copper or fiber connections, 12 or 24 ports with support for IPv6. This product line is soon to be complemented with a next-generation managed switch offering much improved performance. Based upon the latest Broadcom devices, IPv6's lower protocol layers are handled directly by hardware for lower latency and improved throughput.

## Reaching the heart

Bringing effective Ethernet communications to a force on the move will itself be a challenge, requiring vastly more wireless bandwidth than is available today; however, the intention behind the introduction of IPv6 is also to take communications deep into the heart of platforms, their systems, and subsystems. This will facilitate not only the sharing of data, but may also permit the operation and control of sensors, weapons, propulsion, and navigation systems from any remote location or even multiple locations and users. This migration of intelligence and control out of a deployed platform to a war fighter's console could make today's concept of an "onboard embedded intelligent subsystem" redundant, being replaced by a population of simple "remote terminals" instead.

This level of intrusion could well be seen first in small UAVs and Unmanned Combat Aerial Vehicles (UCAVs). In these vehicles, the volume of sensor data that could be acquired requires massive off-board computing resources to process and assimilate into the tactical situation. As a result, the vehicle's mission could be redirected in real time as situations develop. This also offers the potential for security vulnerabilities, but intrusion will inevitably be required anyway for software maintenance and network management just like any other Information Technology (IT) system. While network security will be enhanced by IPv6's encryption, it will still rely heavily on secure, partitioned operating systems such as ARINC-653 and MILS for protection.

## DoD committed to switch

IPv6 has been selected and will be implemented by the DoD, eventually finding a place in every platform, touching most embedded systems in some form or another within the next few years. It may even radically change the way these embedded

systems are implemented. Ethernet switch device technology is on the fast track for more performance through hardware execution of the protocol, fueled by the telcos' desire for more payload through their networks and the division of their services by quality requirements. The DoD will benefit from this rapid growth as will COTS vendors, such as GE Fanuc, and their customers by offering ultra-competitive, mainstream technology solutions for gateways, switched fabrics for platform networks and, eventually, fully integrated systems and subsystems incorporating IPv6.

For more information, contact Duncan at young.duncan1@btinternet.com.

## Special report: MAE show, Ascot (UK)

By Hermann Strass

The UK has Europe's largest military equipment and services market. Each year, record numbers of visitors attend the Farnborough Air Show in southern England. However, so far there was no military aerospace electronics show. For the first time, though, on September 26, 2006, the Military & Aerospace Electronics (MAE) Technical Conference and Exhibition presented *The Future of Electronic Systems for Military and*

This inaugural show was well received by attendees and exhibitors. More than 30 companies demonstrated hardware and software, and several trade magazines including *Military Embedded Systems* and *VMEbus Systems* supported the event. Other supporters included SAE-UK and VITA. There were 18 presentations organized into three tracks (in three theatres) throughout the day. Conference topics included:

- » Designing with COTS

- » Development tools

- » Lead-free issues

- » Microprocessors, controllers, and FPGAs

- » Networks

- » Obsolescence management

- » Power electronics

- » Real-time operating systems and middleware

- » Reliability

- » Rugged electronics

- » Using open standards to design net-centric warfare systems

- » Test and measurement

Presentations were carefully selected by an independent, neutral panel of experts from many applications. The main focus was on the latest developments, technical issues, and

Figure 1

Aerospace at a historic venue west of London. The Ascot Racecourse site, close to Windsor Castle, has large facilities for conventions and exhibitions that are also used as the venue for the world-famous horse races. The traditional red brick style buildings (see Figure 1, courtesy of Technology Consulting) contrast with the modern grandstand (see Figure 2, courtesy of Technology Consulting) where formally dressed gentlemen and ladies with fancy hats would watch the horse races. Obviously, there were no horse races during the time of the military and aerospace electronics show.

Figure 2

## TO GREAT LENGTHS FOR OUR CUSTOMERS.

From the toughest terrains in the universe to the antiseptic environment of the operating room, Hypertronics delivers the highest reliability electronic connectors for our customers' most demanding applications. But our commitment doesn't end there. We provide complete, custom design solutions for customers, including cabling, mechanical design, integrated electronics and electrical modeling capabilities. Hypertronics custom solutions can save you valuable engineering and manufacturing time and ensure the overall reliability of your final product. Our complete solutions are as dependable as our connectors, and our service and support is unmatched. For more information on Hypertronics reliable connectors and dependable solutions, call 1-800-225-9228, email info@hypertronics.com or visit our web site at www.hypertronics.com/wego.html.

## HYPERTRONICS: RELIABLE CONNECTORS. DEPENDABLE SOLUTIONS.

HYPERTRONICS CORPORATION

Hudson, MA 1-800-225-9228 www.hypertronics.com

ISO 9001, AS9100, 13485 & 14001 certified

©2006 OpenSystems Publishing. Not for distribution.

## **Industry Analysis**

implementation decisions for secure and reliable systems in harsh and mission-critical environments. The event was packed with real case studies, practical demonstrations, and highly technical information. A brief overview of selected presentations indicates the wide range of topics covered during this *future-directed* event

## Cooling: Paul Rose, Flomerics

Paul Rose gave a presentation on the simulation of cooling of electrical/electronic components on boards and in systems. Devices and systems are getting smaller all the time, but performance and power stay the same or increase. This means heat is concentrating in smaller volume and has less surface area for dissipation. In military systems, space-limited and environmental conditions are harsh. Cooling (deheating) methods used on commercial systems are therefore insufficient. It would be extremely expensive and time consuming to test many possible configurations by producing real systems, because several iterations would be needed.

Flomerics Ltd., UK, the leader in computer simulation of deheating and cooling methods and designs, has developed FLOTHERM, a Computational Fluid Dynamics (CFD) simulation program and toolset to solve heat transfer design issues without a need to produce real components or systems. CFD is the analysis of systems involving fluid flow, heat transfer, and associated phenomena such as chemical reactions by means of computer-based simulations. A set of (NavierStokes) equations is solved to fully simulate the physics of flow. Only a subset of the possible equations is required to iteratively calculate solutions for electronic systems. It may take about one night to run each simulation. This is not too long, because it would take much longer to produce a board or a system, and to learn that the product still runs too hot. A virtual model can be repeated easily using different parameters.

In addition to adequate deheating, the solution will also be optimal in terms of energy to cool it, noise, and reliability. FLOTHERM software and toolsets are available from Flomerics Ltd. or under license, sometimes using company-specific names from manufacturers and electronic systems integrators.

## COTS: Richard Jaenicke, Mercury Computer Systems, Inc.

Richard Jaenicke gave a detailed analysis of Intel versus PowerPC multiprocessor platforms. A comparison was presented on VMEbus systems meeting COTS industrial requirements. Topics included were Symmetric MultiProcessor (SMP) systems, Non-Uniform Memory Access (NUMA) systems, and other variants.

PowerPC-based systems showed much higher GFLOPS and in some cases higher memory bandwidth than Intel Xeon and Core Duo variants. Interprocessor bandwidth was almost the same for both platforms. PowerPC is enhanced when a large amount of floating-point performance is needed. The Intel platform is better when Multichip SMP is required.

## Lead-free: Ken Hall, Triteq

Ken Hall discussed lead-free topics, which are of particular interest in Europe. Every contractor, manufacturer, or system integrator is confronted with lead-free issues. The market for electronic components in the military and aerospace industry is constantly declining. For instance, the UK market share dropped from 9 percent in 1984 to 0.9 percent in 2005. Currently, Triteq estimates that components are made obsolete at a rate of 13,000 per month.

Some military components are exempt from Restriction of the use of certain Hazardous Substances (RoHS) compliance, but COTS components are not. There are many legal, commercial, and technical issues. A technically competent and quality-oriented partner may be required to provide cost-effective turnkey solutions to obsolescence redesign. Triteq is the only TUV-certified subcontract design house in the UK. It is one of a few design subcontractors in the UK with ISO 13485 certification for safety-critical medical design.

## Networks: Bob Pickles, SBS Technologies, Inc.

Bob Pickles reported about Avionics Full Duplex Switched Ethernet (AFDX), a deterministic and failure-resistant version of Ethernet. AFDX was developed for the Airbus A380 and is currently used on the Boeing B787 Dreamliner. The Airbus A400M (military transporter) and Airbus A350 (civil transporter) will be next to use it. It is a replacement for ARINC 429, using a deterministic protocol as defined in ARINC 664 Part 7. This real-time Ethernet version is switched, eliminating data collisions. The transmission rate is bounded to eliminate loss of packets. Real-time, deterministic operation and a fully redundant transmission channel make AFDX usable in mission-critical systems. Jitter and latency are also bounded to ensure there are no hidden performance problems during operation.

The SBS system, AFDX-E1000, uses standard hardware components and a software stack running in an FPGA. The stack is written in higher-level language. It is very easy to add functions and to transport it to different hardware. A hardware solution would make upgrades lengthy, expensive, and subject to End-Of-Life (EOL) issues. The SBS solution makes the system hardware independent and dynamically upgradeable.

## Reliability: John Jones, IGG Component Technology Ltd.

John Jones presented information about identifying counterfeit components, reliability testing, lead-free issues, and long-term storage of COTS components. Clearly identified second source products, when properly tested and certified, are acceptable to use. However, counterfeit (nonoriginal) components of unknown or low quality are a severe problem in high-reliability systems because what you see is not always what you get.

Technical reliability issues may include corrosion, (silver) metallization migration, intermetallics (gold-aluminum and tin-copper), or fatigue. Quality and reliability testing may include Destructive Physical Analysis (DPA), life testing, accelerated testing, or thermal cycling.

## Industry Analysis -

Preparation for a long-term storage of 20+ years includes stabilization bake at 85 °C for 48 hours, individually sealed components, and storage under specified humidity and temperature conditions.

## Safety: Alex Wilson, Wind River Systems, Inc.

Alex Wilson gave information on MIL/ COTS operating systems requirements. Modern warfare is all about sharing information using IP-based information networks. The Multiple Independent Levels of Security (MILS) architecture specifies compartmentalized hierarchical systems required by the National Security Agency (NSA). These systems include Non-bypassable, Evaluatable, Alwaysinvoked, and Tamper-proof (NEAT). Assured trust levels are required on a component-by-component basis. Changes in noninteracting components need reevaluating of only the changed component, resulting in huge cost savings. The MILS concept benefits from ARINC 653 time and space partitioning, deterministic, predictable execution, and other requirements of this standard. Safety assurance is possible through DO-176B Level A certification. VxWorks RTOS with a MIKS Kernel Layer runs in kernel mode, provides separation and security, and controls information flow between partitions.

## VITA's presentation on standards

Representing VITA Europe at MAE, I reported on standards for industrial and military systems, which have more demanding requirements than commercial systems. They are used for much longer times in hard real-time and deterministic applications. VITA

ommercial systems. They are used for systems for military space applications and deterministic applications. VITA

provides standards for products that have to operate under such conditions. VMEbus technology, which started 25 years ago, was standardized by VITA and is continuously enhanced to meet the increasing demands of military, industrial, and aerospace requirements. A recent major step forward is the introduction of the VITA 46 standard for increased speed (12.5 Gbps), number of transmission circuits, and I/O contacts (728 total). Cooling, reliability, and lead-free issues are also topics of VMEbus technology standardization by the VITA Standards Organization (VSO).

For about 20 years now, VMEbus technology has been and still is the leading open standard for modular computer systems in real-time, high-availability, highreliability applications. New or enhanced standards ensure this will be so for the next 25 years. One project that proves this is VITA 58 Electronics Integration for Level 2 maintenance. Systems will be packed into sealed standardized enclosures called *canisters*. These canisters can be installed or replaced by anyone without operator intervention or system shutdown. This is obviously a standard for very long-term usage. VITA and the VSO provide the standards for these long-term applications.

## **Success at MAE**

The MAE show proved itself effective (see Figure 3, courtesy of Technology Consulting). Attendees left the event with in-depth technical information about state-of-the-art and future electronic systems for military, defense, and aerospace applications.

For further information, e-mail Hermann at hstrass@ opensystems-publishing.com.

Figure 3

## Java technology trends offer renewed promise for portable embedded applications

## By Dave Wood

Because of the promise of increased productivity and reduced error incidence, achieving program portability has always been an important goal in software engineering. The goal of portability has been met with mixed success because of varying approaches to portability from one programming language to another. Further, the special characteristics of embedded, real-time, and safety-critical applications present additional challenges to portability. Dave examines the characteristics of C++, Ada, and Java and their implications for portability in embedded development.

Creating highly portable code is an important mechanism for increasing software development productivity while improving software maintenance and longevity. Today's primary languages for military embedded systems – C++ and Ada – along with emerging embedded Java technology, each provide their own portability characteristics.

## Not all portability is created equal

C and C++ programs often are presumed to be portable. Consider the following code:

#include <stdio.h>

main()

{

printf ("This code is

portable!\n");

}

This piece of code will compile and run on practically every commercial processor/operating system combination in existence. The fact that it will do so is not a reflection of anything inherently portable about the language itself, but rather it is a reflection of the fact that C or C++compilers are available on essentially every platform. As such, C qualifies as a portable language, at least so long as the programs adhere to commonly supported core syntax. Thus C/C++ are portable in the sense of *platform pervasiveness*.

On the other hand, Ada was designed specifically to promote code portability with an emphasis on tightly controlled international standardization and rigorous conformance test suites. Although Ada includes many implementation-dependent features, its portability features provide substantial built-in standard libraries and a standard multi-threaded execution model. As such, Ada also qualifies as a portable language. Yet, although Ada compilers are available on a wide array of platforms, they are not nearly as widely available as C/C++ compilers. Therefore, we consider Ada portable in the sense of platform independence.

C/C++ is portable thanks to ubiquity rather than design. Ada is portable thanks to design rather than ubiquity. These kinds of distinctions form a rich basis for "my language is better than your language" debates among advocates.

## **Defining portability**

Clearly, portability means different things to different people. By evaluating the merits of various portability paradigms against the actual needs of a particular audience, we can make value judgments about the suitability of a given language's portability characteristics. Table 1 lists cross-platform portability factors, and their relative importance is dependent upon individual needs.

Choosing between C++ and Ada offers a trade-off between a more portable design (Ada) and a wider potential pool of available platforms (C++). A third option, Java, offers the promise of both platform pervasiveness and platform independence at the same time.

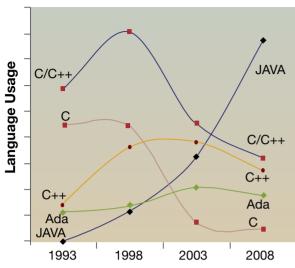

In the nonembedded software community, Java has already emerged as the favorite. Studies indicate that Java popularity has

| Component   | Possible Cross-platform Portability Requirements     |  |  |  |  |  |

|-------------|------------------------------------------------------|--|--|--|--|--|

| Compiler    | Compilers for language exist on required platforms   |  |  |  |  |  |

| Compiler    | Compilers exist and conform to same standard         |  |  |  |  |  |

| Libraries   | Common library types are commercially available      |  |  |  |  |  |

|             | Common libraries inclusive in language standard      |  |  |  |  |  |

| Source Code | Compatible across platforms and OS versions          |  |  |  |  |  |

|             | Compatible across variants of language and libraries |  |  |  |  |  |

|             | GUI code same across platforms without change        |  |  |  |  |  |

|             | No exposed OS or hardware dependencies               |  |  |  |  |  |

| Runtime     | Same runtime API across platforms                    |  |  |  |  |  |

|             | Consistent runtime behavior across platforms         |  |  |  |  |  |

Table 1

## Usage Trends of Ada, C, C++, and Java

Data Source: *Programming Language Trends, An Empirical Study of Programming Language Trends,* Yaofei Chen, PhD dissertation, New Jersey Institute of Technology, August 2003.

Figure 1

overtaken that of C/C++ in enterprise and desktop computing (see Figure 1), and is available on most computing platforms. At the same time, Java's design features mirror and even exceed many of the high-portability characteristics of Ada. This is a reflection of the "Write Once – Run Anywhere" philosophy that drove the design of the Java language, the Java library set, and the Java virtual machine.

As seen in Table 2, C++, Ada, and Java each offers its own strengths. For military embedded applications, the question is which of these options presents the best match to priorities. To help answer that

question, three key areas to consider are source code portability, library portability, and behavioral portability.

## Source code portability

At the source code level, it is certainly possible to write portable C/C++ code, given careful attention coding to practices. However, C/C++ presents many opportunities for making nonportable code. An example of some of thought the processes recommended for C/C++ programmers to improve portability can be found in The C++ Portability Guide (see sidebar).

This publication identifies a number of areas where C and C++ programmers need to tread carefully in order to achieve higher portability.

In contrast to C++, Ada is a rigorously specified language with very well-defined and longstanding international standardization. Even so, Annex M of the language standard identifies more than 100 implementation-dependent aspects of the language that should be carefully encapsulated to facilitate portability.

An example of an area where a programmer needs to take extra care with C/C++

| Portability Factor    | Ada      | C++       | Java      |  |  |  |

|-----------------------|----------|-----------|-----------|--|--|--|

| Platforms             | moderate | pervasive | growing   |  |  |  |

| Standardization       | high     | moderate  | high      |  |  |  |

| Built-in Libraries    | moderate | minimal   | extensive |  |  |  |

| Third Party Libraries | moderate | extensive | extensive |  |  |  |

| Commercial Use        | minimal  | extensive | extensive |  |  |  |

| Runtime Behavior      | defined  | undefined | defined   |  |  |  |

| Safe Programming      | yes      | no        | yes       |  |  |  |

Table 2

is with the type system. C/C++ typing is comparatively loose and implementation dependent. Details of atomic types such as type size (for example, the number of bits in shorts, ints, and longs) as well as "endianness" are implementation-specific. Other nonportable behavior includes the value of uninitialized variables and the results of accessing memory that has been freed. For Java, details and behaviors of this sort are either explicitly defined and abstracted away from the programmer or simply not applicable.

## Library portability

Building complex systems is not practical without the availability of off-the-shelf libraries. Many such libraries exist for all three of the languages discussed herein, but not all are equally portable. Libraries can be considered most portable if they are defined as part of the standard, if the content of the standard libraries is comprehensive, and if the standard is widely adopted across implementations.

In this regard, Java clearly excels to levels far beyond any competing offering. The core Standard Edition libraries alone consist of 166 packages and 3,279 classes. Although the C/C++ ecosystem provides an extensive collection of open source and commercial libraries, the libraries that are inclusive in the language standard are comparatively Spartan. Library support can vary from implementation to implementation and from platform to platform, with the consequence of having an impact on portability.

The standard Ada library set is consistent across implementations and very well-defined. In comparison, the scope of the standardized set of Java libraries is staggering and growing because of the participation of a large, cooperative, and vibrant development community. Like C/C++, Java enjoys a very large ecosystem beyond the standard such as APIs for 3-D graphics, OpenGL, compression, and numerical analysis. Some libraries have achieved quasi-standard status and ubiquitous availability. An example of this is the SWT graphics library from the Eclipse Foundation.

## The C++ Portability Guide

(www.mozilla.org/hacking/portable-cpp.html)

- 1. Be very careful when writing C++ templates.

- Don't use static constructors.

- 3. Don't use exceptions.

- 4. Don't use runtime type Information.

- 5. Don't use C++ standard library features, including iostream

- 6. Don't use namespace facility.

- 7. main() must be in a C++ file.

- 8. Use the common denominator between members of a C/C++ compiler family.

- 9. Don't put C++ comments in C code.

- 10. Don't put carriage returns in XP code.

- 11. Put a new line at end-of-file.

- 12. Don't put extra top-level semicolons in code.

- 13. C++ filename extension is .cpp.

- 14. Don't mix varargs and inlines.

- 15. Don't use initializer lists with objects.

- 16. Always have a default constructor.

- 17. Be careful with inner (nested) classes.

- 18. Be careful of variable declarations that require construction or initialization.

- 19. Make header files compatible with C and C++.

- 20. Be careful of the scoping of variables declared inside for () statements.

- 21. Declare local initialized aggregates as static.

- 22. Expect complex inlines to be nonportable.

- 23. Don't use return statements that have an inline function in the return expression.

- 24. Be careful with the include depth of files and file size.

- 25. Use virtual declaration on all subclass virtual member functions.

- 26. Always declare a copy constructor and assignment operator.

- 27. Be careful of overloaded methods with like signatures.

- 28. Type scalar constants to avoid unexpected ambiguities.

- 29. Always use PRBool for boolean variables in XP code.

- 30. Use macros for C++ style casts.

- 31. Don't use mutable.

- 32. Use nsCOMPtr in XPCOM code.

- 33. Don't use reserved words as identifiers.

The C++ Portability Guide was made available for distribution under the Creative Commons License (http://creativecommons.org/licenses/by-sa/2.0/).

## When It Comes to Him,

"It" is information. And as a leading supplier of High-Performance Analog, Digital, and Serial I/O, we offer Large FIFOs, Large FPGAs and the Highest Bus Speed in the industry.

Get the Free

Mission Critical Report:

Top Ten Things to

Remember

Before Specifying

a Data Acquisition Board

Call about our Free Loaner Board offers.

Fast Is Not Good Enough.

VME PMC PCI 104+ cPCI

RSC# 21 @www.mil-embedded.com/rsc

General Standards Corporation

High Performance Bus Interface Solutions

REAL-TIME REAL-FAST

Phone: 800-653-9970 Fax: 256-880-8788 www.generalstandards.com

## Behavioral portability

Even if portability is achieved at the source code level and at the library level, the runtime behavior of a program may be very different from one platform to another. In the case of C/C++, runtime behavior is undefined. C/C++ does not specify mechanisms for execution threads, priorities, or even interprocess communications. Thus, these types of issues are relegated to the operating system, and the interfaces are application-specific.

In contrast, both Java and Ada specify a clear runtime semantic. Java goes further than Ada in specifying not only semantics related to thread execution and communication, but also in defining an abstracted operating system complete with its own virtual machine code and memory management known as *byte code* and *garbage collection*, respectively.

For a particular application, all of these runtime characteristics may be fully implemented within the Java Virtual Machine, or may be partially mapped to underlying operating system functionality where available. In any case, the application code is unaware of the implementation layer, and so is completely portable.

It is this sense of portability that makes Java so attractive for embedded development: It is intrinsically much easier to move from one real-time operating system to another, making mission-critical developers much less dependent on, and less locked into, a particular RTOS supplier.

Even with Java's high level of portability, there remain behavioral characteristics that are not consistent across platforms. Most notably, the Java standard does not specify thread timing behaviors, nor predictability of garbage collection activities. These deficiencies generally are not a concern for desktop and enterprise applications but are a major hindrance to the spread of Java to real-time and embedded applications where timing and predictable runtime behavior are critical.

Technologies such as real-time garbage collection and predictable thread semantics, which are embodied in Aonix's PERC Virtual Machine, provide the behavior required for mission-critical applications while remaining fully portable thanks to syntactic compatibility with Java standards. In the realm of hard realtime behaviors, new technologies have been developed that provide precise memory management and hard real-time guarantees suitable for highly constrained and safety-critical applications. These updates to the Java standard are being developed under the umbrella of the Java Community Process [JSR 302 - Safety Critical Java Technology]. This effort is being directed by the Open Group with the cooperation of key companies including Sun, Boeing, Aonix, Rockwell Collins, and Siemens.

Similarly, abstract interfaces for "close to the silicon" activities such as interrupt handling, memory mapping, and device control are being developed based on specifications that are friendly to cross-platform portability.

## Java's portability reduces risk, increases productivity

As embedded applications become increasingly complex, placing the burden of source code, library, and behavioral portability on developers is increasingly risky and nonproductive. It also results in software that is more error-prone and more costly to maintain. Although C++, Ada, and Java each have strengths in terms of portability, the capabilities offered by Java technologies are inherently more productive and scalable, and therefore represent a better long-term bet for embedded systems development.

## **Graphics pose portability problem**

One of the biggest obstacles to portability for desktop and enterprise applications is at the GUI level. Traditionally, GUIs have been application-specific both in characteristics and in terms of the API. A measure of portability can be achieved by building an abstraction layer that is consistent across platforms. Underneath, the abstracted API binds to the underlying graphics engine, such as the Win32 API for Windows, or a flavor of X11 on UNIX or Linux platforms. Traditionally, the GUI has been considered to be tightly tied to the operating system because that operating systems' users are sensitive to a particular look and feel and expect a consistent functionality across applications on their platform.

Neither C/C++ nor Ada provide a standard GUI API, leaving questions of GUI-specific bindings outside the scope of the language. In contrast, Java incorporates GUI APIs (Swing and AWT) directly in the standard. Applications written to the Swing standard ought to have high portability between conforming platforms through the use of a common API. As mentioned previously, the SWT API, defined as part of the open-source Eclipse libraries, offers another portable graphics interface that is widely used by Java programmers. Whereas the goal of Swing is to offer a consistent cross-platform look and feel, the goal of SWT is to offer cross-platform portability with a look and feel matching that expected on the target platform. Which is better is a matter of opinion, but both offer a means to source code portability.

Increasingly, complex embedded applications require more sophisticated graphics capabilities, yet these applications continue to be demanding in terms of performance and footprint characteristics. Swing solutions, typically mapped to a native GUI such as X11, are usually too big, slow, and unpredictable for use in mission-critical embedded applications. Specialized embedded graphics engines such as PEG+ from Swell Software are a more appropriate fit. SWT bindings to PEG+ exist, offering the high performance needed for multi-platform embedded applications while also accentuating portability.

Dave Wood has been involved with realtime and embedded software for more than 25 years. His activities have included analysis, design, coding, testing,

research, and marketing of technology in commercial avionics, telecom, defense, multimedia, software tools, and consumer electronics applications. Dave has worked for Lear Siegler, General Electric, SofTech, ComLogic, and the Software Engineering Institute at Carnegie Mellon University, and presently serves as marketing director for Aonix. He holds a BA from Kalamazoo College.

### Aonix

5930 Cornerstone Court W, #250 San Diego, CA 92121 858-824-0254 • Fax: 858-824-0212 dave.wood@aonix.com www.aonix.com

# Your community resource for VME-industry news, user groups, and the VME blog We will be a series of the series of

## Safety-critical Java enhances reliability while reducing test and certification costs

By Ole N. Oest, DDC-I

Java provides an excellent environment for developing embedded software. Until now, however, Java has been too big, complex, and unpredictable for safety-critical applications. To address this shortcoming, the Safety-Critical Java Expert Group (JSR 302) (http://jcp.org/en/jsr/detail?id=302) is working on a subset of real-time Java that will make it easier to develop reliable, deterministic code suitable for safety-critical applications requiring FAA certification.

The Java Community first addressed the real-time limitations of Java when it convened the Real-Time for Java Expert Group (RTJEG) in 1999, which developed the Real-Time Specification for Java (RTSJ). This specification, an extension of The Java Language Specification and The Java Virtual Machine Specification, enhances real-time responsiveness by introducing mechanisms for preemptive scheduling and priority inversion avoidance, and providing tools that allow tasks to avoid garbage collection delays.

The Safety-Critical Java Expert Group will further refine the RTSJ, making it suitable for safety-critical applications with the most demanding testing requirements. In particular, the Safety-Critical Java Expert Group will trim the RTSJ spec, ensuring that conforming safety-critical applications can be run without requiring a garbage collector or heap at all, and ensuring that the rigors of FAA certification to DO-178B level A can be met.

As a member of the Safety-Critical Java Expert Group, Phoenix-based tool developerDDC-I,Inc.(www.ddci.com/pr) will be drawing on its pioneering work in developing the Ada 95 specification, which is the "gold standard" for safety-critical programming languages. DDC-I will also bring to bear its extensive FAA DO-178B experience, which is the "gold standard" for certifying safety-critical systems.

Ole N. Oest is the chief operating officer of DDC-I, Inc., a manufacturer of safety-critical software development tools for more than 20 years. Ole can be contacted at ooest@ddci.com.

## Custom real-time kernels versus COTS Real-Time Operating Systems

By Alex Polmans and David Mosley

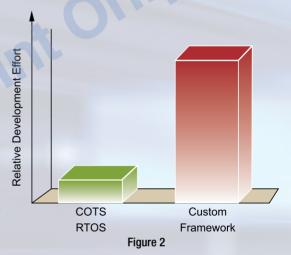

Embedded systems need framework software such as an operating system, communication stacks, and device drivers, but choosing whether to purchase an RTOS or develop a custom framework is not an easy decision. Development time and effort must be weighed against the needs of certification testing in order to determine the most cost-effective approach to follow. Making the wrong choice early in the development effort can carry a significant time and cost penalty. Development tools can help defer that choice until it becomes clearer.

Software has become the dominant cost factor in today's embedded systems, leaving design teams with a critical choice: make or buy? The choice may not be as simple as it first appears, however, especially for the framework code needed by safety-critical applications. The interplay of factors such as development effort and certification testing requires careful consideration when choosing between a commercial operating system and custom-developed software. The right development tools can help.

## The custom vs. COTS choice

To keep software costs at a minimum, and to maximize system reliability, software should be optimized for the design. Optimized software contains only the code for performing the required tasks, and no more. This code has two elements: application code and framework code. Application code handles all of the application-specific data analysis and manipulation tasks, while framework code provides common support functions such as task scheduling and the interface to resources such as hardware, I/O, storage, and user interfaces. Application code is typically custom-written; however,

because the framework will be common between multiple applications, it may be bought as a library or provided as part of the development environment.

The way to create an optimized framework is to assemble it from a combination of small, reusable existing code modules obtained either commercially or from prior projects, and then add new, custom-written code elements. By thus implementing only the bare bones of a framework, developers can ensure that the framework is as small as possible, and contains only the essential support code required by the application. The bare bones framework code may also be simpler to test and more reliable than full-blown commercial software. Because of its size and general purpose nature, a commercial operating system often contains unused and sometimes unexpected pathways that can create surprising behaviors during development and add time and complexity to certification testing.

Still, choosing the buy option for software has several advantages. A COTS Real-Time Operating System (RTOS) may contain nearly every framework element that a system might require. Moreover, these elements are already integrated and tested. Eliminating the integration and testing of framework elements from the development task can save from one to six months of effort on average. Although the COTS framework code may be far from optimal in size, its completeness and robustness reduces project software development to application development alone.

A hybrid option exists for obtaining partially-optimized software: strip COTS software of unneeded elements. Many RTOS vendors offer mechanisms for removing unneeded elements from the RTOS during compilation. Typically these mechanisms take the form of software switches that the developer invokes during the build and compilation processes. These switches may be coded as **#defines** in C header files, or set in XML files, and specify which elements to include in or remove from the generated output.

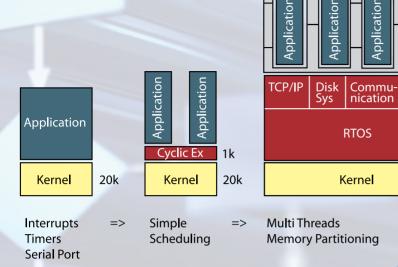

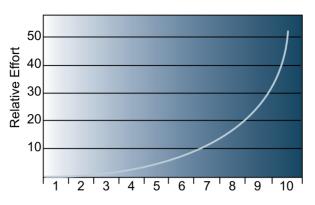

The amount and granularity of the "whittling" that is possible varies with the vendor. Often, the options are too global to provide a high degree of optimization. For example, the disk subsystem of one popular OS contains more than 100 library elements, and developers cannot pick-and-choose among those elements. Even if a project requires only one portion of the disk subsystem, the OS will provide the entire subsystem, leaving a lot of surplus "meat" on the "bare bones." The reduced version may be lighter than the full-scale RTOS, but the size and complexity are still far greater than needed, as illustrated in Figure 1. Custom bare bones framework software, even with scheduling included, requires far less code than the typical COTS RTOS. This size reduction can translate into significant savings during testing.

## **Optimization still required**

The importance of having optimized code has changed subtly over the past decade. Code's impact on system memory requirements used to be the dominant factor in determining how much optimization was necessary. But both memory size increases and cost-per-bit decreases have been so dramatic that memory is not usually a significant factor in the makeversus-buy trade-off for any but the most resource-sensitive systems. The dominant factors now are development effort and certification testing.

pplication

**CORBA**

200k

20k

### Figure 1

## Development effort considerations

Development effort increases dramatically as a function of system software's complexity. To gauge if a project is simple enough to not require a full-blown RTOS, consider the framework services that its software requires. A basic runtime operating system, for instance, provides a scheduler for organizing tasks, timers to support scheduling, a program loader to activate the application code, and basic communications such as a serial port or keypad. The application itself is not necessarily trivial, but as long as its demands for services are simple, a basic runtime kernel may be sufficient and custom software may provide the lowest cost alternative.

The same holds true for systems that run multiple applications, as long as the applications do not interact. In such cases, adding a round-robin time scheduler can account for the additional applications without adding significant complexity to the software. As with the single application, developers can readily support multiple, independent applications with a basic, custom runtime OS.

When system requirements include multiple, interdependent applications, however, a COTS RTOS becomes the stronger candidate. While any competent programmer can create a cyclic task scheduler or serial interface, systems that must handle multiple concurrent tasks with interrupt-driven re-entry or must provide an Internet-compatible protocol stack need programmers with specific expertise in these areas. If such expertise is not available in-house, it must be sought and acquired from outside, delaying that aspect of project development. If the expertise is available in-house, applying

those personnel resources to develop the framework software may not be a profitable use of their time. Their work on the framework makes them unavailable to work on the application code, which is usually where a product's added value resides.

The COTS RTOS is also a good choice for systems that need to support downloadable applications. Creating framework software that can handle applications without knowing in advance what the applications will require can quickly become an overwhelming task. Similarly, a COTS RTOS may also be the best way of handling security requirements such as preventing downloaded applications from interfering with one another. For example, an ARINC 653 compliant RTOS, can guarantee that downloaded applications are separated by both time and memory space partitioning so that there in no risk of one application gaining access to

another's data or other resources. Both the development time and expertise requirements of complex systems, then, favor purchasing a COTS RTOS to provide framework code. As illustrated in Figure 2, the effort it takes to add a COTS RTOS into the system can be as low as one to two weeks (mostly for training on the new software), while developing and integrating a custom framework can take substantially longer. The final system code using the RTOS is suboptimum in terms of its size and complexity, however.

## Consider certification and test costs, too

That added software complexity can have a financial impact. In addition to development efforts, test and certification costs must be examined when considering the make-versus-buy decision. These costs include all of the unit and system testing needed to validate that the software functions as intended, and the documentation artifacts required to verify the software's compliance with applicable guidelines, standards, and regulations. Unfortunately, in the make-versus-buy decision for software, development and test cost considerations can often come into conflict. A decision that reduces one can trigger a significant increase in the other.

The cost and difficulty of FAA certification, for instance, unilaterally increases as a function of code size and the consequences of an undetected error. Such costs can be as great as three times

## Software—more os options open up

the cost of development for safety- or mission-critical system software, where certification standards often require that testing exercise all possible combinations of execution pathways through the software, regardless of whether or not they are expected to occur during normal software operation. As shown in Figure 3, the number of test steps needed in these cases increases exponentially with the number of branch statements (N), for

example, by  $2^N$ . Thus, the surplus code of a COTS RTOS can greatly increase the amount and cost of the certification testing, outweighing the savings in reduced development effort.

The hybrid approach of reducing the COTS RTOS may not be an option. Safety-and mission-critical software standards often require the complete removal of unused code from the system. By not

allowing *dead* code, these standards seek to avoid problems that might occur if a system glitch causes normally dormant code to get executed. Removal of all dead code may be difficult or impossible with a COTS RTOS.

The need for safety and certification testing, therefore, tends to favor custom development. Yet, the results are not clear cut. Custom development leads to smaller code, which leads in turn to reduced testing. On the other hand, COTS software may already have achieved certification. Commercial RTOSs, for example Wind River's VxWorks Platform for Safety Critical and LynuxWorks' LynxOS-178 are precertified, so that their certification costs are spread across multiple customers, reducing the burden on a specific project. Depending on the nature of such certification, its applicability in supporting project certification, and the cost savings involved, precertified COTS software may actually prove to be costcompetitive with custom software in the testing stage.

## Tools reduce risk

The complex and interrelated factors of development time and certification costs are not amenable to simple decision making, yet the choice is critical to minimizing total project costs. The risk of making the wrong choice is high, especially because such choices are often made in the early stages of system software development. Later, when system needs have become clearer, the choice is less risky. As a result, development teams should consider an approach that helps defer the COTS versus bare-bones choice.

Development tools offer this type of approach. Tools such as DDC-I's SCORE are OS-agnostic, meeting standards such as ARINC 653, Eclipse, and POSIX for producing portable code. Such tools allow application code to be developed without first choosing the operating system that the code will run under, freeing teams from the risks of locking in an RTOS choice early in the project. They achieve this flexibility by providing a software switch to use at compilation time that directs the compiler's output to conform

RSC# 26 @www.mil-embedded.com/rsc

to whichever application programming interface the user indicates, whether a COTS RTOS or the small runtime kernel that DDC-I supplies. This flexibility can provide developers with the freedom to delay the makeversus-buy and what-to-buy decisions until the project's needs are stable and clear.

## Waiting clarifies choice

The complexity of the makeversus-buy decision still remains, but having the opportunity to develop the application software first

removes much of the risk. Development tools that allow the application code to remain independent of the operating system provide that opportunity. With the application code in hand, the suitability of each operating system option becomes clearer. Then, making the choice between a COTS RTOS and a custom bare-bones

## **Test Effort**

Relative Code Size Figure 3

approach becomes a comparison of development and test costs.

Alex Polmans, Senior Software Engineer at DDC-I, Inc., has 15 years of experience as a software engineer in naval systems

and 5 years' experience in software tools and runtime development for DDC-I.

He holds a BSc in Engineering (Electronics) and a BSc (honors) in Computer Science from the University of Natal, South Africa.

David Mosley is a Senior Software Engineer at DDC-I, Inc. He has 28 years of experience in compiler development,

specializing in embedded environments. He holds an MS in Computer Science from the University of Arizona.

## DDC-I, Inc.

1825 E. Northern Avenue, Suite 125 Phoenix, AZ 85020 602-275-7172 sales@ddci.com www.ddci.com

## Nothing empowers performance like PowerMP!

The PowerMP concept is designed to provide off-the-shelf and off-the-chart performance for your critical computing needs in demanding environments. Each MP system is a high-performance, low-cost COTS-based multiprocessor computing solution based on industry standards and Pentium and/or PowerPC architecture.

## The new PowerMP6 - a multi-Pentium, ready-to-use solution

When you place a premium on software productivity and performance turn to the turnkey computer system that sizzles—PowerMP6. The newest in the PowerMP line, the PowerMP6 consists of multiple Pentium-M boards in a 19-inch rack. Running Red Hat Linux on the Intel processors supports software productivity and portability through an extensive set of open source and commercial tools and libraries. Performance is dictated by the number of Pentium M processors the system runs and the PowerMP6 available in various customized configurations of up to eight processor boards in a rack.

The PowerMP6 features optimized message passing interface (MPI) for multiprocessor communications and contains software tools geared for such tasks as real-time performance analysis, remote control operations and monitoring system management.

## The PowerMP4-60 - RapidIO™ system entry

The PowerMP4 fills the embedded industry's need for reliability, increased bandwidth and faster bus speeds. It combines PowerPC and Pentium-M technology and takes advantage of the outstanding compute power to power dissipation ratio of the PowerPC technology as well as the wide spectrum of software tools available on PC platforms. PowerMP4-60's RapidloTM high-performance and packet-switched interconnect technology meet your demanding embedded system needs.

## The specialists in embedded performance